從圖紙到鋼材 農(nóng)產(chǎn)品展廳項目中的一體化建設(shè)方案

在現(xiàn)代農(nóng)業(yè)產(chǎn)業(yè)化與鄉(xiāng)村振興的背景下,農(nóng)產(chǎn)品展廳作為展示地域特色、促進商貿(mào)流通、提升品牌形象的重要載體,其建設(shè)需求日益增長。一個成功的展廳項目,始于精細的設(shè)計藍圖,成于扎實的施工建設(shè),而高品質(zhì)的建筑材料,尤其是鋼筋產(chǎn)品,則是確保其結(jié)構(gòu)安全與耐久性的基石。本文將圍繞“農(nóng)產(chǎn)品展廳效果圖與施工圖一套”以及“建筑用鋼筋產(chǎn)品銷售”這兩個核心環(huán)節(jié),闡述如何實現(xiàn)從設(shè)計概念到實體建筑的無縫銜接與高質(zhì)量落地。

一、 設(shè)計先行:效果圖與施工圖——項目的靈魂與骨架

1. 效果圖:描繪愿景,激發(fā)共鳴

農(nóng)產(chǎn)品展廳的效果圖不僅僅是外觀的預(yù)覽,更是項目理念與功能的視覺化呈現(xiàn)。優(yōu)秀的效果圖應(yīng)能:

彰顯特色:巧妙融入地方農(nóng)耕文化、特色農(nóng)產(chǎn)品元素(如麥穗、藤蔓、果實等抽象造型),使建筑本身成為一張立體名片。

功能可視化:清晰展示內(nèi)部空間布局,如產(chǎn)品陳列區(qū)、體驗互動區(qū)、洽談區(qū)、多媒體影音區(qū)等,讓客戶提前感知流暢的參觀動線與豐富的展示體驗。

* 營造氛圍:通過燈光、材質(zhì)、景觀的搭配,營造出自然、質(zhì)樸、科技或奢華等不同格調(diào)的氛圍,契合農(nóng)產(chǎn)品品牌定位。

一套出色的效果圖是打動投資方、獲得審批并與公眾溝通的強大工具。

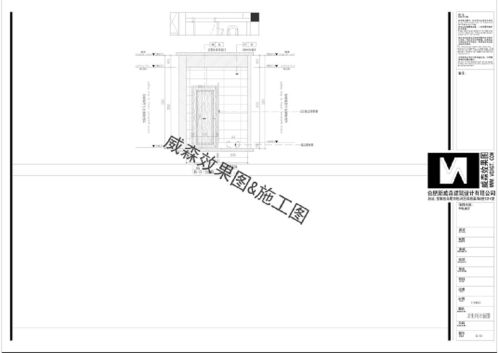

2. 施工圖:精準落地的技術(shù)保障

施工圖是將效果圖轉(zhuǎn)化為現(xiàn)實的根本依據(jù),是指導所有施工活動的法律與技術(shù)文件。一套完整的施工圖應(yīng)包括:

建筑施工圖:總平面圖、各層平面圖、立面圖、剖面圖及詳圖,明確空間尺寸、墻體門窗、裝飾做法等。

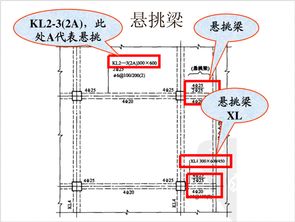

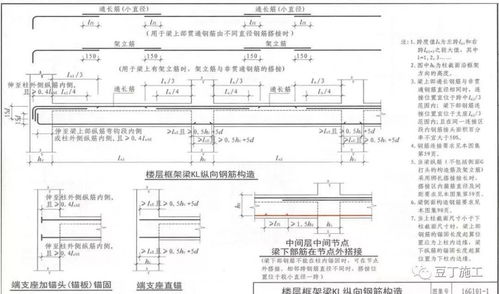

結(jié)構(gòu)施工圖:基礎(chǔ)圖、梁板柱配筋圖、結(jié)構(gòu)詳圖等,這是建筑用鋼筋產(chǎn)品直接應(yīng)用的藍圖,精確規(guī)定了鋼筋的規(guī)格、型號、數(shù)量、布置位置與連接方式。

* 機電施工圖:給排水、電氣、暖通、智能化等專業(yè)圖紙,保障展廳運營的舒適性與先進性。

對于農(nóng)產(chǎn)品展廳,施工圖需特別考慮大型展品運輸通道、特殊溫濕度控制區(qū)域(如冷鏈展示區(qū))的結(jié)構(gòu)與設(shè)備預(yù)留,以及可能的活荷載要求。

二、 材料為基:建筑用鋼筋——支撐安全的隱形力量

當施工圖設(shè)計完畢,項目便進入材料采購與施工階段。其中,鋼筋作為混凝土結(jié)構(gòu)的“骨骼”,其質(zhì)量直接關(guān)系到展廳建筑的整體安全、抗震性能與使用壽命。

1. 鋼筋產(chǎn)品在展廳建設(shè)中的關(guān)鍵應(yīng)用

基礎(chǔ)與地梁:承受整個建筑荷載,需使用高強度、耐腐蝕的鋼筋,確保地基穩(wěn)固。

框架柱與梁:形成主體支撐結(jié)構(gòu),尤其在大跨度展示空間(如無柱大廳)中,對鋼筋的強度、延性和焊接性能要求極高。

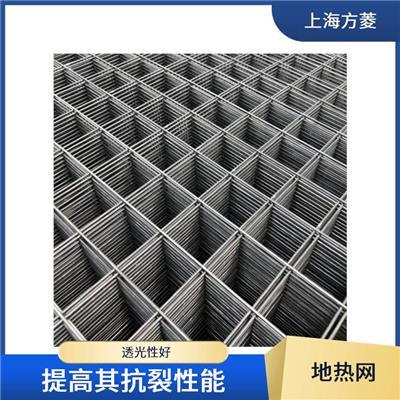

樓板與屋面板:提供使用平面并傳遞荷載,鋼筋網(wǎng)片的鋪設(shè)質(zhì)量直接影響樓板抗裂與平整度。

特殊構(gòu)造:如弧形墻體、懸挑結(jié)構(gòu)、采光頂棚等特色設(shè)計部分,可能需要定制形狀的鋼筋或預(yù)應(yīng)力鋼筋技術(shù)。

2. 如何選擇與銷售適配的鋼筋產(chǎn)品

作為鋼筋銷售方,為農(nóng)產(chǎn)品展廳類項目服務(wù),需超越簡單的產(chǎn)品推銷,提供專業(yè)解決方案:

- 精準解讀施工圖:與施工方、設(shè)計方緊密溝通,深刻理解結(jié)構(gòu)設(shè)計意圖,準確計算所需鋼筋的品種(如HRB400E、HRB500E)、規(guī)格、數(shù)量。

- 保障材料質(zhì)量:提供符合國標(GB/T 1499.2)的優(yōu)質(zhì)產(chǎn)品,附帶質(zhì)量證明書,確保可追溯性。對于有特殊防腐、防火要求的區(qū)域,能提供相應(yīng)產(chǎn)品建議。

- 提供配套服務(wù):可提供定尺加工、彎曲成型等服務(wù),減少現(xiàn)場加工損耗,提高施工效率。確保物流及時,配合施工進度。

- 技術(shù)咨詢支持:能就施工圖中可能存在的鋼筋排布難點、節(jié)點構(gòu)造等提供專業(yè)意見,成為項目的材料技術(shù)伙伴。

三、 協(xié)同共贏:設(shè)計與材料的無縫對接

一個成功的農(nóng)產(chǎn)品展廳項目,離不開設(shè)計與材料供應(yīng)鏈的高效協(xié)同。

- 設(shè)計階段考慮材料特性:設(shè)計師在繪制結(jié)構(gòu)施工圖時,應(yīng)充分了解當前市場主流鋼筋產(chǎn)品的性能參數(shù),使設(shè)計既安全經(jīng)濟又便于采購與施工。

- 材料供應(yīng)反饋優(yōu)化設(shè)計:鋼筋銷售商憑借豐富的項目經(jīng)驗,可以在早期介入,就材料供應(yīng)的可行性、經(jīng)濟性向設(shè)計方提出建議,優(yōu)化選型。

- 貫穿項目全周期:從效果圖的概念呈現(xiàn),到施工圖的精確標注,再到工地現(xiàn)場鋼筋的綁扎澆筑,設(shè)計與材料共同構(gòu)成了項目建設(shè)的連續(xù)鏈條。清晰的效果圖確立目標,詳細的施工圖提供路徑,而優(yōu)質(zhì)的鋼筋產(chǎn)品則是鋪就這條路徑的堅實基石。

###

“農(nóng)產(chǎn)品展廳效果圖施工圖一套”與“建筑用鋼筋產(chǎn)品銷售”,看似是產(chǎn)業(yè)鏈上的兩個獨立環(huán)節(jié),實則緊密相連,共同指向一個目標:打造一個既美觀震撼又安全穩(wěn)固的農(nóng)產(chǎn)品展示與交流平臺。優(yōu)秀的圖紙設(shè)計賦予了建筑靈魂與形態(tài),而可靠的鋼筋產(chǎn)品則鑄就了其強健的體魄。唯有兩者深度融合、專業(yè)協(xié)作,才能確保每一個農(nóng)產(chǎn)品展廳從紙面藍圖完美落地為標志性實體,在展現(xiàn)現(xiàn)代農(nóng)業(yè)風采的經(jīng)得起時間的考驗,真正服務(wù)于鄉(xiāng)村產(chǎn)業(yè)振興的長遠發(fā)展。

如若轉(zhuǎn)載,請注明出處:http://www.j548.cn/product/65.html

更新時間:2026-04-14 08:31:24